半導体は現代生活に欠かせないものです。

ここ数年で半導体の重要度の認識が広がりニュースや新聞などで取り上げられることも増えています。

そんな半導体ですが、製造工程は非常に複雑です。半導体を製造する工場はクリーンルームになっており、チリやホコリが大敵のため工場見学は通常できません。

この記事では半導体どのようにしてできるのかの工程について誰にでもわかるように解説します。

ぜひとも最後までご覧ください。

【プロフィール】

- 上場企業の現役半導体プロセスエンジニア

(経験10年以上) - 多くの材料メーカーや生産委託先企業との業務経験あり

- 著書を出版しました

- 詳しいプロフィールはこちらからどうぞ

- 半導体に興味関心がある

- 半導体を勉強したい学生さんや社会人の方

動画で解説:半導体ができるまでの工程

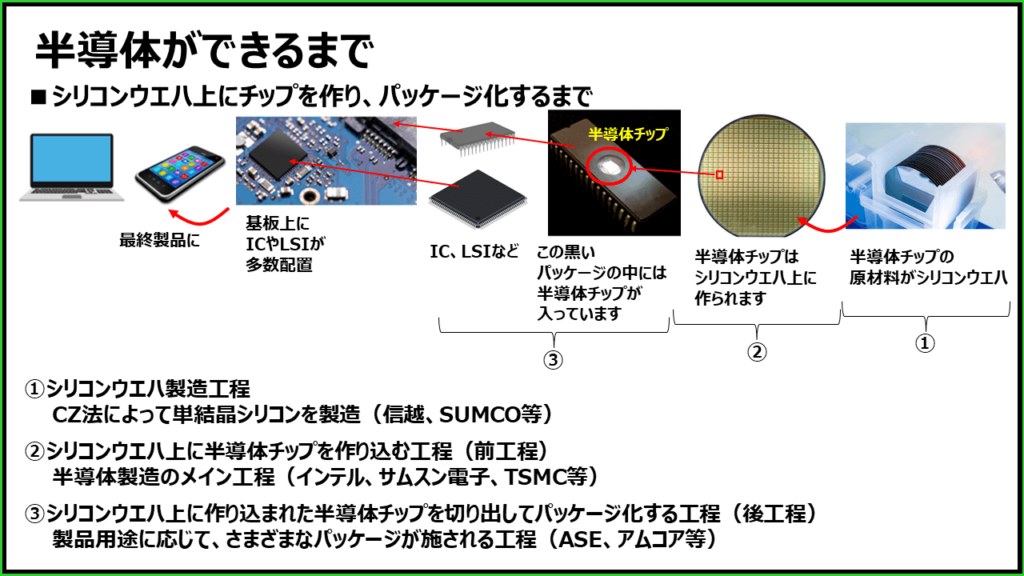

半導体ができるまで

まずは現代生活に欠かすことができない、「半導体」ができるまでを最終製品から逆にみていきましょう。

私たちが普段使っているパソコンやスマホの中には、黒色や緑色をした基板上に電子部品が多数搭載されています。

その中にICやLSIがあり、これらの中に半導体チップが入っています。

半導体チップはシリコンウエハ上に作り込まれます。

半導体チップができまでの工程を分解しますと、以下の3工程です。

- シリコンウエハができるまで(シリコンウエハ製造工程)

- シリコンウエハ上にチップを作り込むまで(前工程)

- チップを切り出してパッケージ化するまで(後工程)

この3工程の全体を説明していきます。

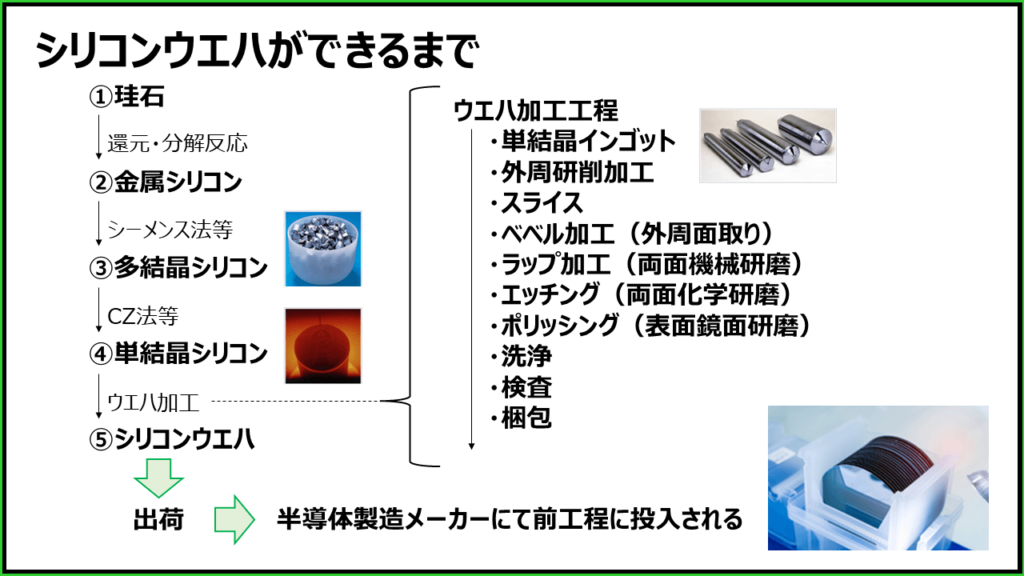

シリコンウエハができるまで

シリコンウエハとは、シリコン単結晶の薄い円盤状の基板のことです。

シリコンウエハ上に半導体チップ(=IC)が作り込まれます。

シリコンウエハができるまでは大きく5つのステップに分かれます。

まず原料となる珪石を採取します。珪石は河原に転がっている白い石ですが、シリコンの含有量が高い海外製の珪石が使われます。

珪石を還元分解反応によって金属シリコンにします。この時点での純度は98~99%程度です。

還元分解反応には電気炉を使って行います。この処理には電気代が高い日本では採算性が合わないため製造せず、すべて海外で生産されています。

次に金属シリコンをシーメンス法などを用いて多結晶シリコンにします。

金属シリコンに水素と四塩化珪素を反応させてトリクロロシランとし、トリクロロシランを蒸留精製して純度を極限まで高めた後に、反応炉で水素と反応させてシリコンを析出されるというものです。

ここで半導体グレードまたはイレブンナインと呼ばれる超高純度のシリコンになります。

多結晶シリコンを材料にして単結晶シリコンのインゴットを製造します。

単結晶シリコンインゴットはCZ法(チョクラルスキー法)などで製造されます。

最後に単結晶シリコンのインゴットをスライス(切断)し、研削や研磨を行ってシリコンウエハが完成し、半導体製造メーカーへ出荷されます。

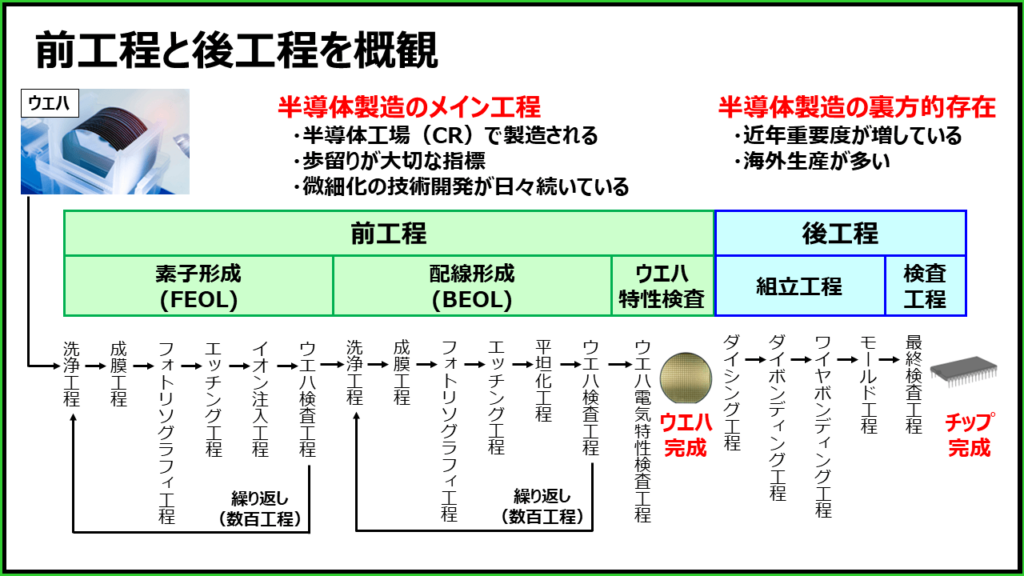

前工程と後工程

シリコンウエハ上に半導体チップを作り込む前工程と、そのチップをパッケージ化する後工程の全体像をみてみましょう。

前工程はその中で大きく3つの工程に分けられます。

まずは素子形成工程です。FEOLとも呼ばれます。

ここではCMOSなどの素子を形成する工程です。

洗浄、成膜、フォトリソグラフィ、エッチング、イオン注入、ウエハ検査といった各工程を繰り返して素子形成がなされます。

次は配線工程です。BEOLとも呼ばれます。

ここでは素子と素子をつなぐ配線を形成します。

ここでも洗浄や成膜、フォトリソグラフィ、エッチング、平坦化、ウエハ検査の各工程が繰り返し実施されます。

そしてウエハの電気特性検査を行い完成します。

後工程は大きく2つの工程に分けられます。組立工程と検査工程です。

ウエハからチップを切り出してパッケージ化するまでが組立工程で、パッケージ化されたICの最終検査が検査工程になります。

前工程は半導体製造のメイン工程でクリーンルームで製造されます。

あとで説明する歩留りが重要な指標で、微細化が技術的なポイントです。

後工程は裏方的な存在でしたが、近年ではその重要度が増しています。

その理由としては微細化はまだまだ続いていますが、物理的な限界は必ず訪れます。そのため3次元的な実装などのより高集積な半導体開発が進められているためです。

東南アジアを中心とした海外生産が多いのも特徴です。

半導体工場内はクリーンルーム

半導体製造においてチリやホコリは不良の原因となるため大敵です。

そこで半導体製造ではほとんどの工程がクリーンルーム内で行われます。

半導体工場の中では多くの装置が整然と並び、先端の工場では多くの作業が自動化されており人の作業はあまりありません。

ウエハが格納されたキャリアを天井のOHTで運び、装置に自動的に仕掛けられます。

ただし古い工場ではそこまでの自動化がなされていないところも多くあり、人の作業によって装置への仕掛けなどが行われています。

半導体工場の構成要素としては、大きく3つあります。

- メインとなる工場棟

- 工場エンジニアや事務員が作業する事務棟

- 工場に必要な外回り(電力・ガス・水・薬液設備)

半導体工場では多くの電力やガス、水、薬品を扱います。そのため外回りの設備の保守管理も重要になります。

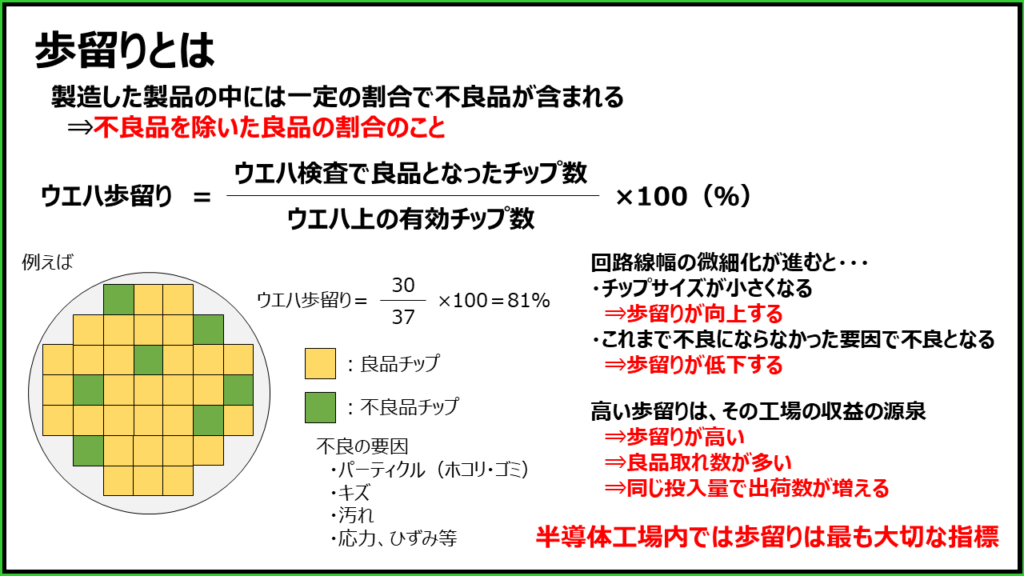

歩留りは半導体工場で最も大切な指標

歩留りとは製造したウエハの中で良品になった割合のことです。

半導体では歩留り100%ということは基本的にありません。どうしても不良チップが発生してしまいます。

その要因はさまざまでチリやホコリなどのパーティクル付着やキズ、汚れ、応力にひずみなどがあげられます。

また微細化が進むと同じ機能を持ったチップであればチップサイズが小さくなり、歩留りは向上しますが、微細化によってこれまでは不良にならなかった要因で不良化することがあり、歩留り低下の原因となります。

歩留りが高いことは工場の収益の源泉となるため、工場エンジニアは歩留り向上に日々勤しんでいます。

そのため半導体工場において歩留りは最も重要な指標と言っても過言ではありません。

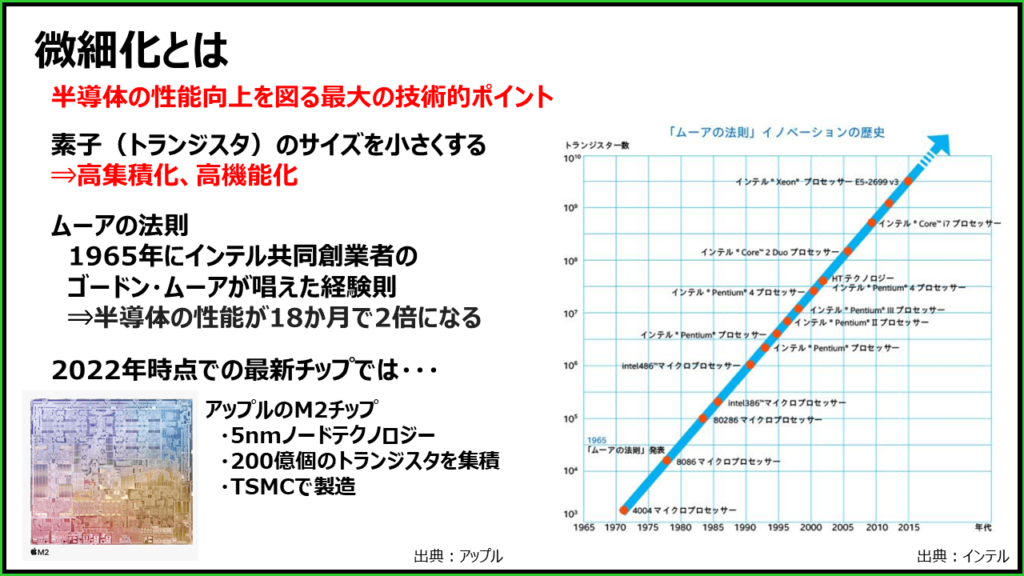

微細化は性能向上を図る技術的ポイント

ニュースで報道される半導体の微細化で○○nmという言葉があります(○○には数字が入る)。

微細化とは半導体の性能向上を図る技術的ポイントで素子(トランジスタ)のサイズを小さくすることです。

素子サイズを小さくすることで高集積化が可能になり素子の高機能化を実現できます。

微細化に関してはムーアの法則という有名な法則があります。

これはインテル共同創業者の1人であるゴードン・ムーアが1965年に唱えた経験則で半導体の性能(集積度)が18カ月で2倍になるというものです。

実際にインテルのプロセッサではムーアの法則に従って(ムーアの法則に則ることを目指して)技術開発がなされてきました。

2022年時点の最新チップではアップルのM2チップがTSMCの5nmプロセスを使って200億個のトランジスタを集積しています。

前工程の各要素技術

ここからは前工程の各要素技術をみていきましょう。

さまざまな工程が繰り返し行い半導体を製造していきます。

各工程の技術をみてから実際にCMOSの製造工程フローでどのように使われているかをあとで確認しましょう。

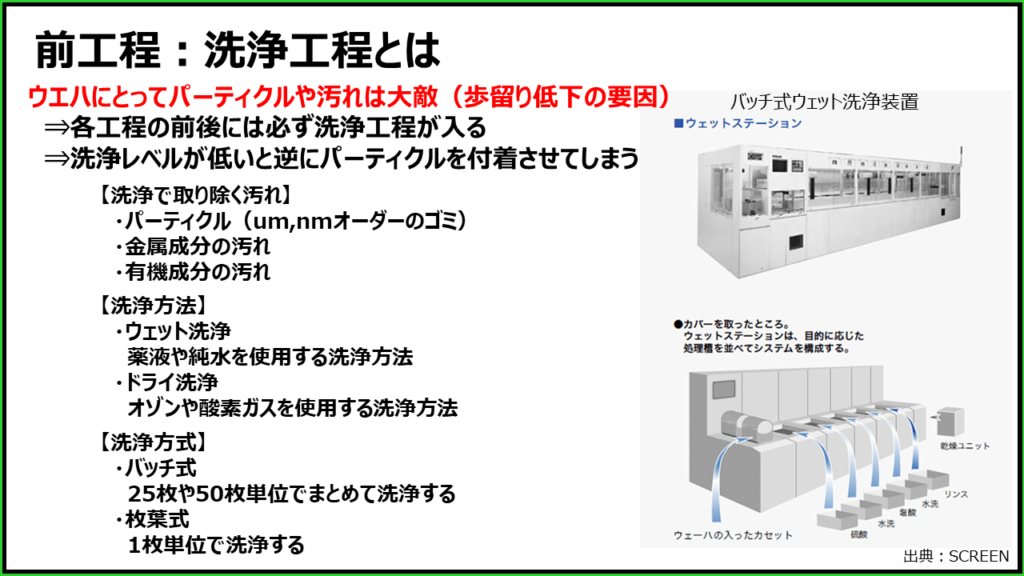

洗浄工程

まずは洗浄工程です。

半導体製造においてウエハ上のチリやホコリといったパーティクルや汚れは歩留り低下の要因となるため大敵です。

そのため成膜などの各工程の前後には必ず洗浄工程が入ります。

ただしこの洗浄工程のレベルが低いと逆にパーティクルなどを付着させてしまうことがありますのでその点にも注意が必要です。

洗浄工程で取り除く汚れはum、nmオーダーのパーティクルや有機成分、金属成分の汚れです。

それぞれの目的に応じた薬液を使い分けることで除去します。

洗浄方法は大きく2つあります。1つはウェット洗浄で薬液や純水を使って洗浄する方法です。過去から一般的に使用されてきた手法です。

もう一つはドライ洗浄でオゾンや酸素ガスを使うことで洗浄する方法です。

洗浄方式としてはバッチ式と言われる25枚や50枚単位でまとめて洗浄する方法と枚葉式という1枚単位で洗浄する方法があります。

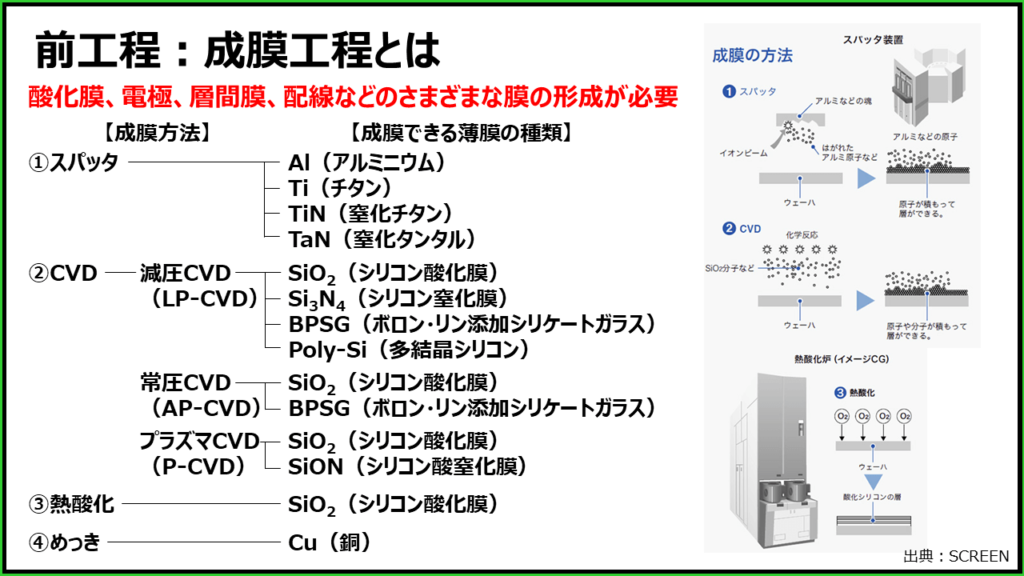

成膜工程

次は成膜工程です。

成膜工程では酸化膜や層間膜、配線などのさまざまな膜を形成します。

成膜方法には大きく4つあります。

1つ目はスパッタリング法でスパッタとよく略されます。

スパッタは超高真空化でターゲット(堆積させたい膜の素)にアルゴン原子を高エネルギーでぶつけて弾き出されたターゲット構成原子をウエハ上に付着させることで成膜する方法です。

AlやTiなどの配線層の成膜に使用されます。

2つ目はCVDです。

CVDはChemical Vapor Depositionの略称で日本語では化学気相成長法と言います。

CVDでは成膜する膜の種類に応じた原料ガスをチャンバ内に入れ、化学触媒反応を利用して成膜する方法です。

この触媒反応に必要なエネルギーの与え方によって熱CVDとプラズマCVDに分かれます。

さらに熱CVDは大気圧で実施する常圧CVDと大気圧よりも低い減圧状態で実施する減圧CVDに分かれます。

CVDは製膜できる膜種が多く酸化膜や窒化膜、層間膜として使われるBPSGなどを成膜することができます。

3つ目は熱酸化です。

熱酸化法は最も伝統的な成膜方法です。

ウエハを高温の酸化炉に入れて酸素ガスによってシリコンと酸素を反応させてシリコン酸化膜を成長させる方法です。

4つ目はめっきです。

めっきは配線材料に銅を利用する場合に必要不可欠な手法です。

めっきでは硫酸銅などのめっき液にウエハを浸漬させて電解めっきを施すことによってウエハ表面に銅薄膜を析出させる方法です。

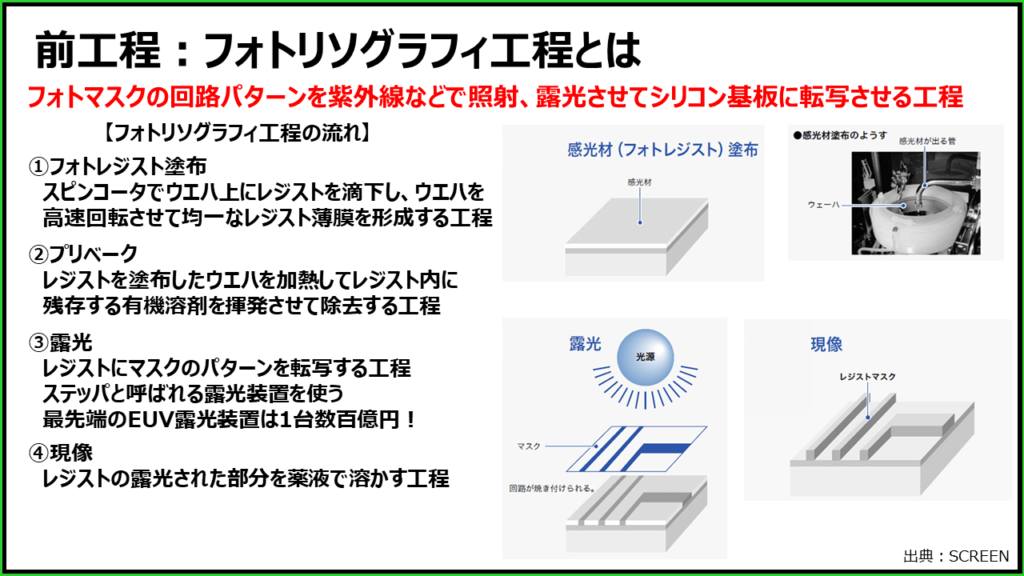

フォトリソグラフィ工程

フォトリソグラフィ工程は前工程のメイン工程と言ってもいいかもしれません。

フォトマスクの回路パターンをウエハ上、または成膜した薄膜上に紫外線などで照射、露光して転写する工程です。

フォトリソグラフィ工程では、デジタルカメラ以前に使われていた銀塩カメラと同様の原理を利用しています。

フォトリソグラフィ工程の流れとしては、以下の4ステップです。

スピンコータと呼ばれる装置でウエハ上にレジストを滴下してウエハを高速回転させることで均一なレジスト薄膜を形成します。

ウエハを加熱させることでレジスト内に残存する有機溶剤を揮発させて除去します。

露光によってレジストにマスクパターンが転写されます。露光装置はステッパと呼ばれる装置を使いますが、最先端プロセスで使用されるEUV露光機は1台が数百億円もする装置です。

レジストの露光された部分を現像液で溶かします。

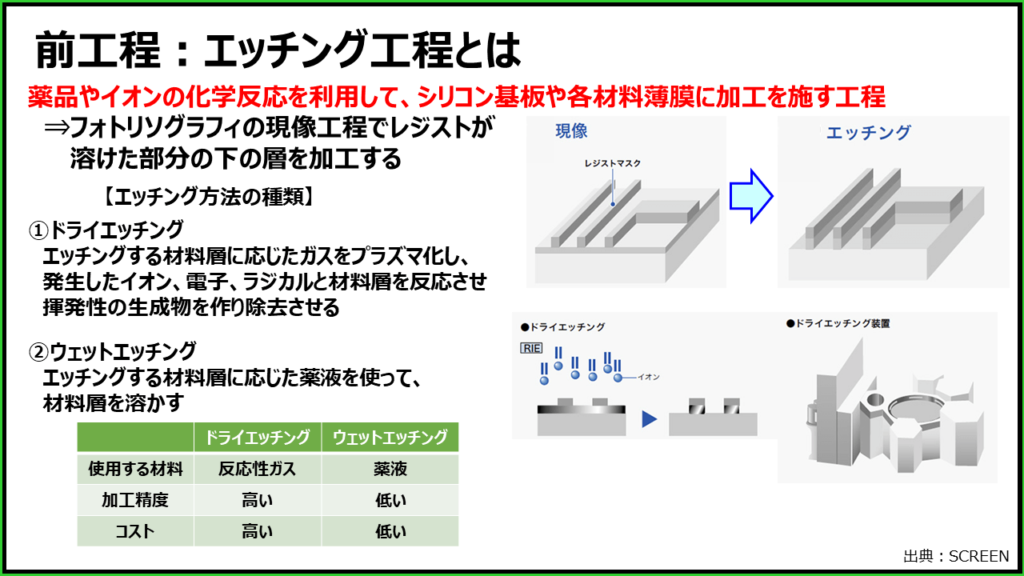

エッチング工程

エッチング工程はフォトリソグラフィ工程で形成した回路パターンに沿ってシリコンや薄膜材料に形状加工を施す工程です。

エッチング方法は大きく2種類あります。

1つ目はドライエッチングでエッチングする材料層に応じたガスをプラズマ化させて発生したイオンや電子、ラジカルと材料層を反応させて揮発性の生成物を作ることで除去します。

もう1つはウェットエッチングで薬液を使って材料層を溶かすことで除去します。

一般的にドライエッチングは加工精度は高いですがコストも高くなります。

ウェットエッチングは加工精度はドライエッチングと比べるますと低くなりますが、コストを抑えることができます。

その工程で必要な加工精度によって使い分けられています。

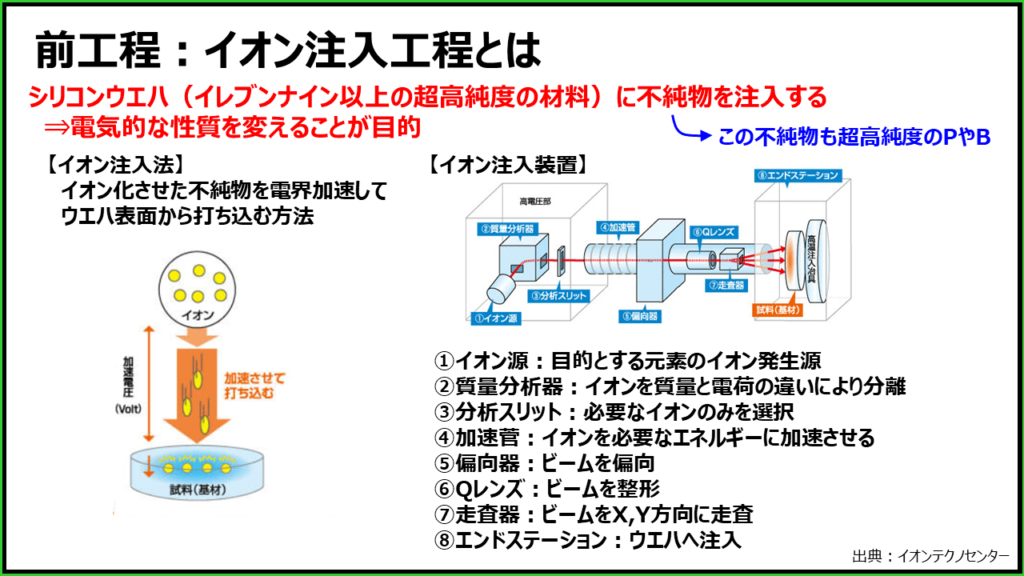

イオン注入工程

イオン注入工程はウエハに不純物を注入させることによって電気的な特性を変える工程です。

ここで言う不純物はシリコンに対して異なる物質という意味であり、注入する不純物自体も超高純度なリンやボロンなどです。

シリコンは周期表で第Ⅳ族の元素で、超高純度なシリコンウエハの状態では電圧をかけても電流はほとんど流れません。

ここに第Ⅴ族のリンや第Ⅲ族のボロンなどを注入することによって電流の担い手となる電子やホールを発生させ電気が流れるようになります。

イオン注入法とはその名の通り、イオン化させた不純物を電界加速してウエハ表面から文字通り叩き込む手法です。

加速させるエネルギーやイオン量によって工程設計者の意図した通りの分布を実現させることができます。

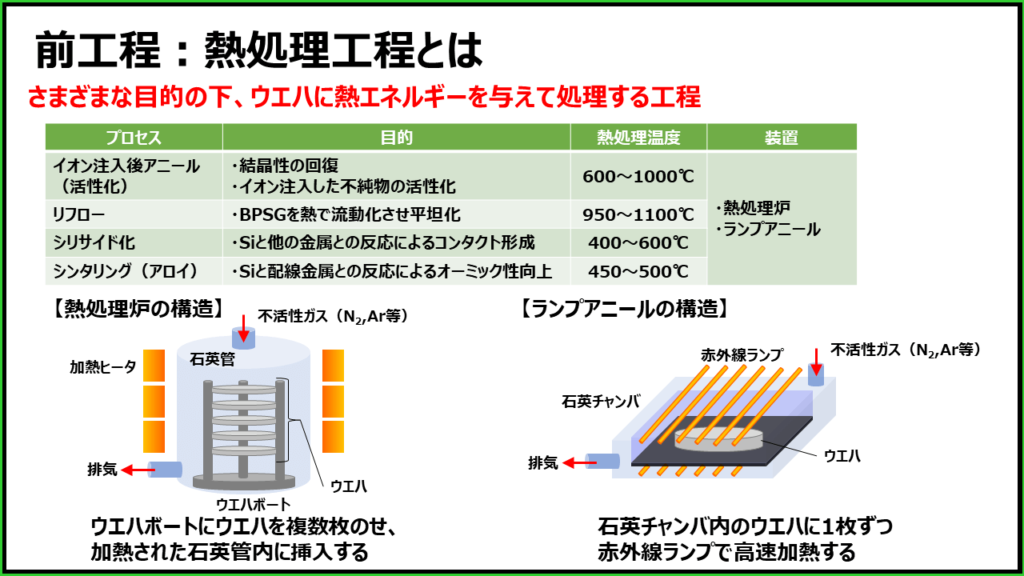

熱処理工程

熱処理工程とはさまざまな目的に応じてウエハに熱エネルギーを与える工程のことです。

例えばイオン注入後アニールではイオン注入によって壊れた結晶の回復や注入した不純物を活性化させるために行います。

またBPSG成膜後のリフローではBPSGに熱を加えることで流動化させて平坦化させることを目的に行います。

熱処理工程では炉またはランプアニール装置を使います。炉であればウエハボードにウエハを複数枚のせて処理しますので多くのウエハをまとめて処理できます。いわゆるバッチ処理です。

ランプアニール装置では1枚ずつ赤外線ランプで高速加熱する枚葉処理です。

ウエハに熱を加える時間や面内の均一性など求められる精度に応じて装置を使い分けます。

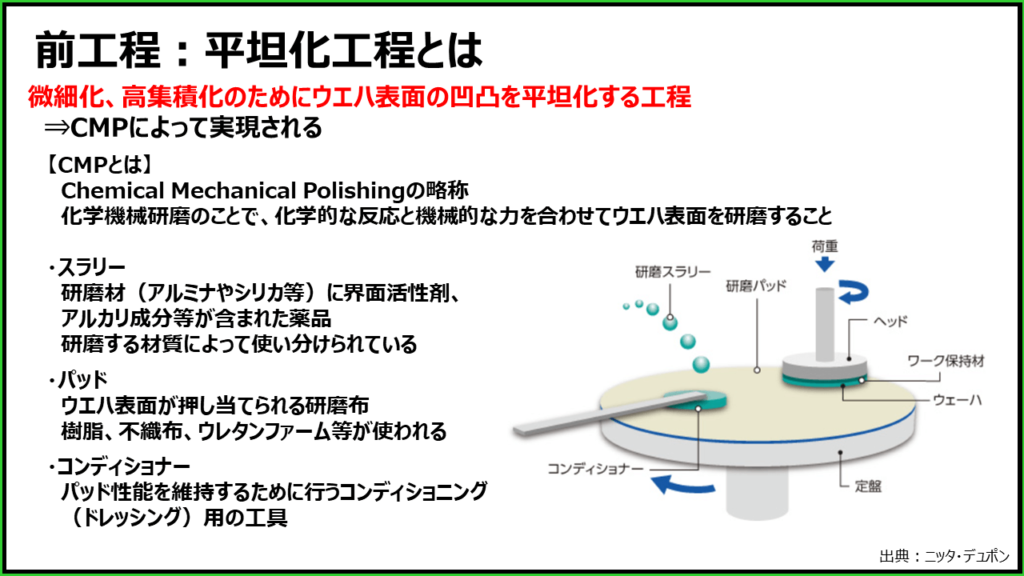

平坦化工程

平坦化工程はウエハ表面の凹凸を平坦にするための工程です。

ウエハ表面に凹凸ができると2つの問題が発生します。

- 1つはフォトリソグラフィ工程において凹凸があることでフォトレジストを均一に塗れなくなったり、露光時に焦点距離が変動するために微細な回路パターンの転写ができなくなることです。

- 2つ目は配線形成時に凹凸があることで被覆性が悪くなり配線の断線が生じることです。

これらの問題を解決するために使われるのがCMPです。

CMPはChemical Mechanical Polishingの略称で、日本語では化学機械研磨と言います。

化学的な反応と機械的な力を合わせてウエハ表面を研磨することです。

スラリーと呼ばれる研磨液を流しながらヘッドに下向きに貼り付けたウエハの表面を常盤上の研磨パッドで研磨します。

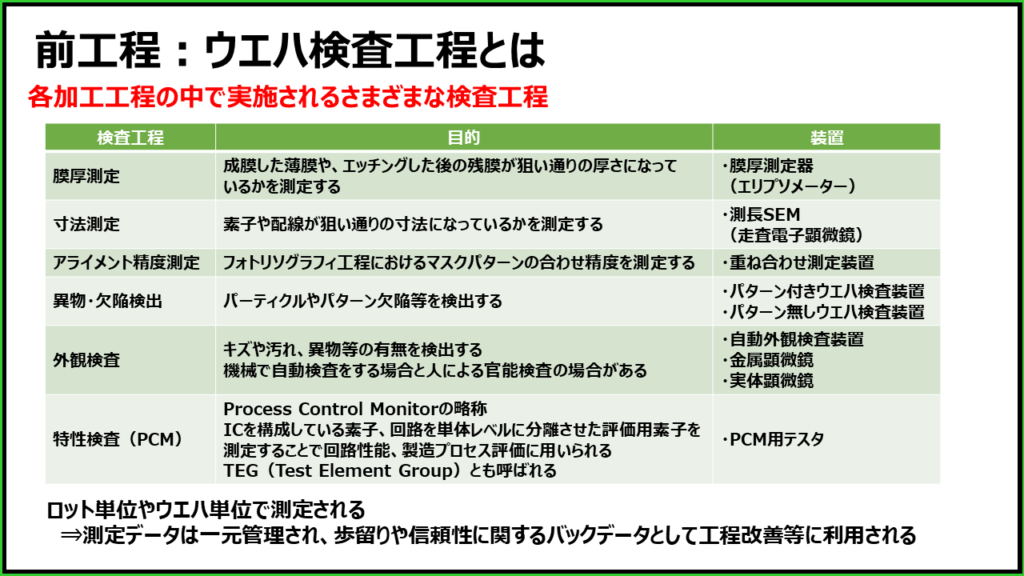

ウエハ検査工程

ウエハ検査工程はこれまでご紹介した各加工工程の中で実施されるさまざまな検査工程です。

膜厚測定は成膜やエッチングした残膜の厚さを測定する工程です。同じように寸法測定は狙い通りの寸法になっているかを測定します。

アライメント精度測定はフォトリソグラフィ工程におけるマスクパターンの合わせ精度を測定します。異物・欠陥検査は不良の要因となるパーティクルやパターン欠陥を検出します。

外観検査はキズや汚れの有無を検出します。自動外観検査装置を使って自動で実施する場合と、外観検査員による官能検査の場合があります。

特性検査はPCMやTEGと呼ばれ、ICを構成している素子や回路を単体レベルに分離させた評価用素子を作り込んでおくことで回路性能や製造プロセスの評価に使われます。

素子レベルで要求通りのものができているかがわかります。

これらの検査はロット単位またはウエハ単位で測定されます。

測定されたデータは一元管理されて歩留りや信頼性に関するバックデータとして工程改善等に利用されます。

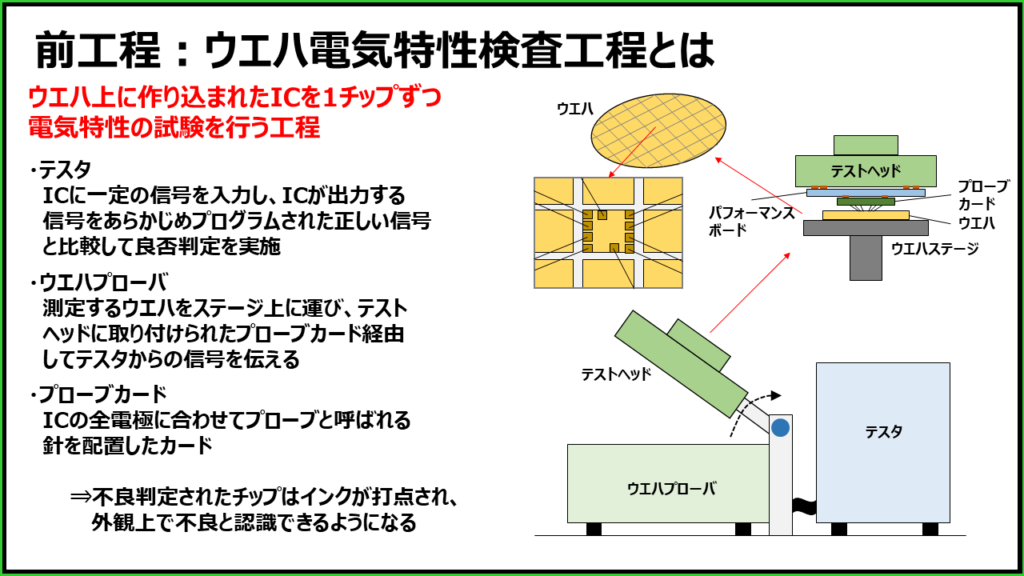

ウエハ電気特性検査工程

ウエハ電気特性検査工程はウエハ上に作り込まれたICを1チップずつ電気特性試験を行う工程です。

ウエハプローバのステージ上にウエハを載せ、プローブカードから伸びている針をICの電極に当ててテスタから電気信号を入力してICが出力する信号をあらかじめプログラムされた正しい信号と比較して良否判定を行います。

不良判定されたチップはチップ上にインク打点され、見た目として不良と認識できるようになります。

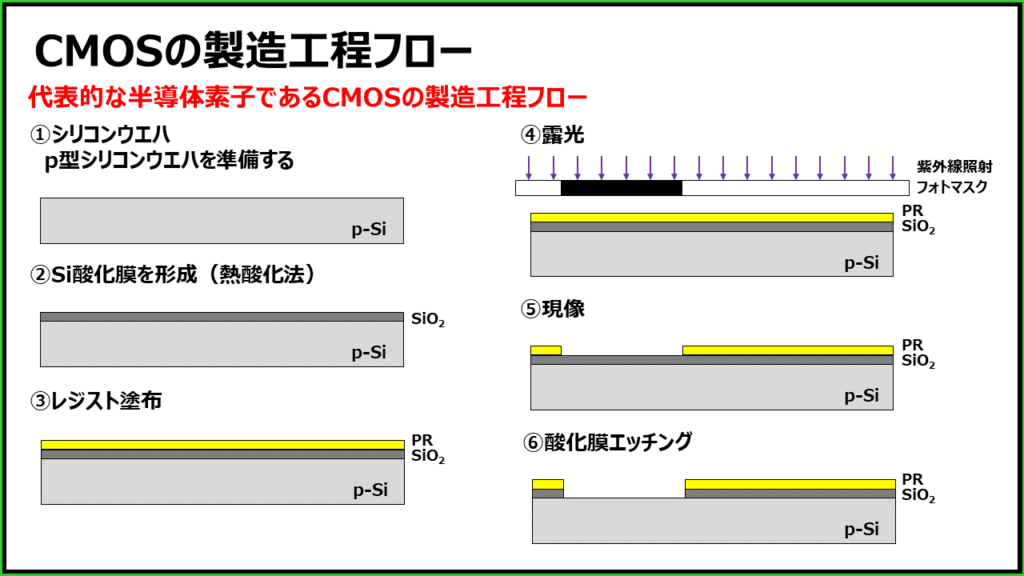

CMOS製造工程フロー

ここまで半導体製造に必要な各加工技術や検査技術をみてきました。

とは言え、実際の製造工程フローはなかなかイメージしにくいと思います。

ここでは代表的な素子であるCMOSの製造工程フローの概略を断面図をみながら説明していきます。

①まずはシリコンウエハを用意します。

②熱酸化法でシリコン酸化膜を形成します。

③レジストを塗布します。

④フォトマスクを使い露光します。

⑤現像します、紫外線が当たらなかった場所のレジストが溶解してなくなります。

⑥レジストがなくなった部分の酸化膜をエッチングします。

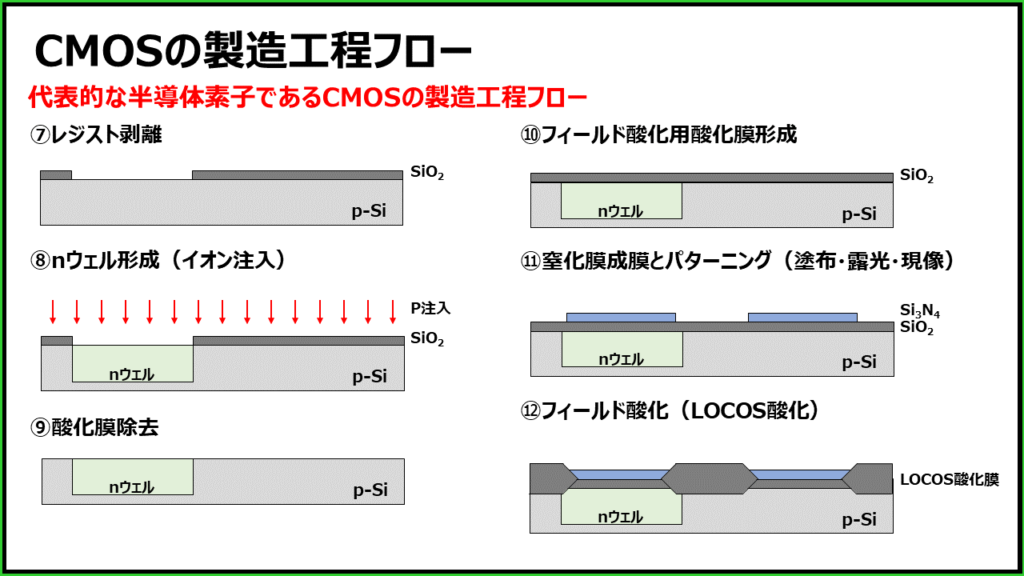

⑦不要になったレジストを薬液を使って剥離します。

⑧イオン注入法によってnウェルを形成します。酸化膜が残っている部分は酸化膜がマスク代わりとなることでイオン注入はされません。

⑨酸化膜を除去します。

⑩酸化膜を形成し直します。

⑪窒化膜をCVD法によって成膜し、パターニング(レジスト塗布、露光、現像、エッチング)します。

⑫LOCOS酸化をします。LOCOSとはLOCal Oxidation of Siliconの略称で、素子間の分離用の厚い酸化膜です。窒化膜が形成されている部分は酸化されません。フィールド酸化とも呼ばれます。

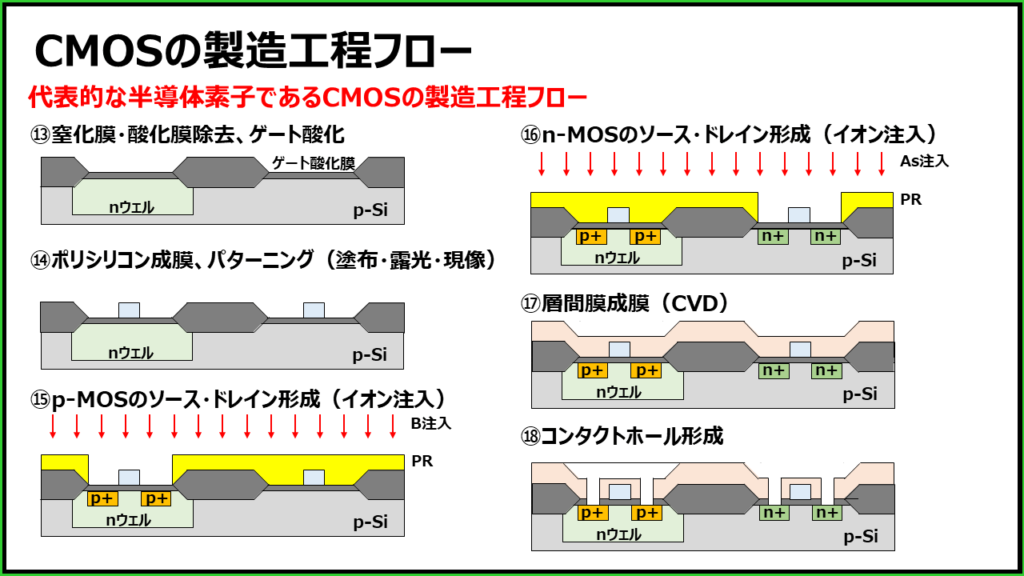

⑬窒化膜と窒化膜下の酸化膜を除去し、ゲート酸化膜を成膜します。

⑭ゲート電極となるポリシリコンを成膜しパターニングを行います。

⑮レジストをマスクにしてイオン注入してp-MOSのソース、ドレイン形成をします。

⑯同様にn-MOSのソース、ドレイン形成をします。

⑰層間絶縁膜をCVD法で成膜します。

⑱コンタクトホールを形成して、電極の通り道を確保します。

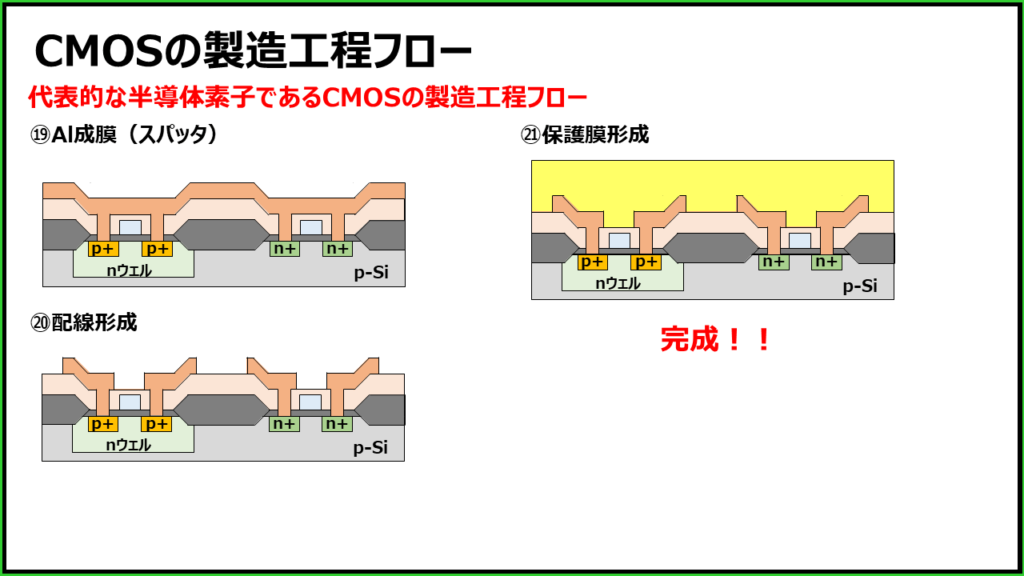

⑲配線となるAlをスパッタで成膜します。

⑳配線をパターニングします。

㉑保護膜を形成して完成です。

後工程の各要素技術

ここからは後工程の各要素技術をみていきます。

前工程に重点を置いたため、かなり簡易的になっていますがご了承ください。

ダイシング工程

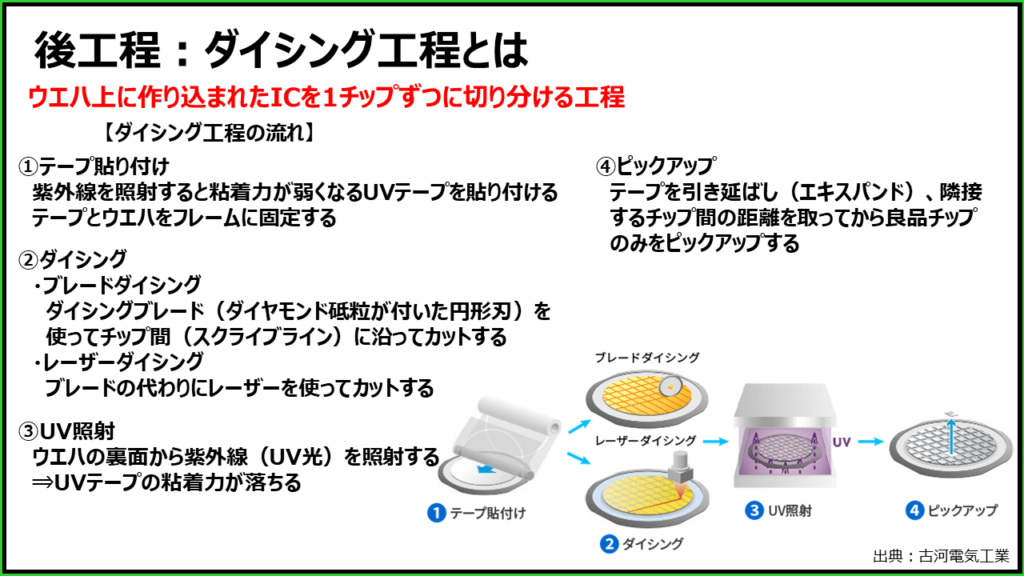

ダイシング工程はウエハ上に作り込まれたICを1チップずつに切り分ける工程です。

UVテープをウエハに貼り付け、テープとウエハをフレームに固定します。

ダイシング方法には大きく2種類あり、ダイヤモンド砥粒が付いた円形刃を使うブレードダイシングと、ブレードの代わりにレーザーを使うレーザーダイシングがあります。

ダイシングできたらUV光を照射します。

これでUVテープの粘着力が落ちます。

テープを引き延ばして隣接するチップ間距離を取ってからインクが打たれていない良品チップだけをピックアップします。

組立・検査工程

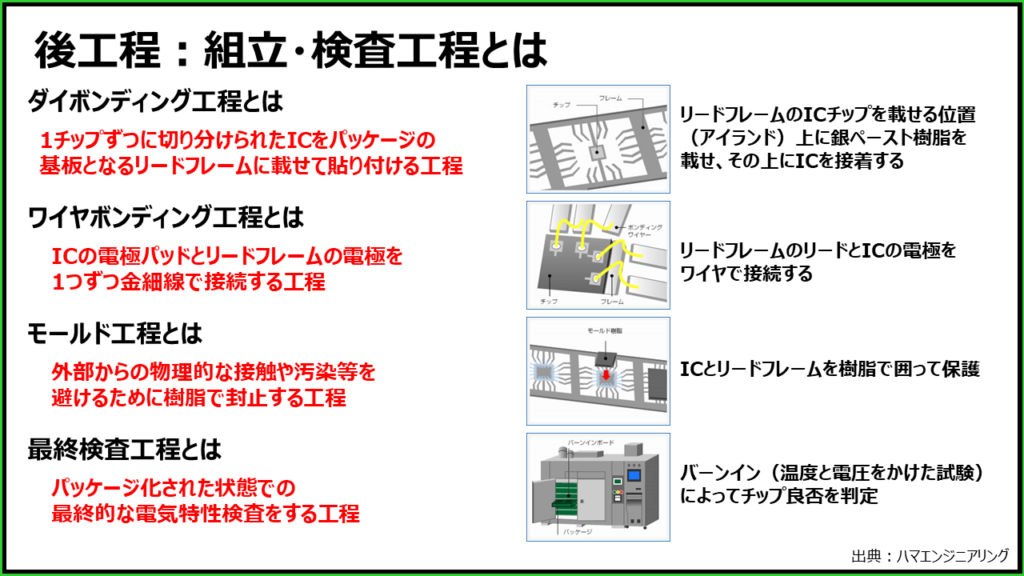

組立工程はダイボンディング工程、ワイヤボンディング工程、モールド工程で構成されます。

ダイボンディング工程ではリードフレームと呼ばれるフレームの中心にあるICチップを載せます。

銀ペーストなどを使ってリードフレームとICを接着します。

ワイヤボンディング工程ではリードフレームのリードとICの電極を金ワイヤで接続します。

モールド工程では、外部からの物理的な接触や汚染等を避けるために樹脂でチップ全体を封止します。

こまで来るとようやく黒い塊から足が出ているパッケージ化された格好になります。

最後に最終検査を行います。

パッケージ化された状態で電気特性検査を行います。バーンインと呼ばれる温度と電圧をかけた試験が行われます。

検査を合格したICが出荷されて、家電やスマホ、PCや自動車等々の最終製品へと組み込まれていきます。